# A Fully Non-Volatile Reconfigurable Magnetic Arithmetic Logic Unit Based on Majority Logic

<sup>1</sup>J. Kavitha, <sup>2</sup>Singamsetty Gowtham, <sup>3</sup>Shaik Yasin, <sup>4</sup>Padamata Leela Sai,

<sup>5</sup>Vankayala Srinivasa Reddy

<sup>1</sup>Associate Professor, Dept Electronics and Communication Engineering, St.Ann's College of Engineering and Technology, Nayunipalli (V), Vetapalem (M), Chirala, Bapatla Dist, Andhra Pradesh – 523187, India

<sup>2,3,4,5</sup>U. G Student, Dept Electronics and Communication Engineering, St.Ann's College of Engineering and Technology, Nayunipalli (V), Vetapalem (M), Chirala, Bapatla Dist, Andhra Pradesh – 523187, India

## ABSTRACT

*The growing demand for energy-efficient and high-performance computing systems has driven research toward non-volatile logic architectures. Conventional CMOS-based Arithmetic Logic Units (ALUs) suffer from high leakage power and volatility, leading to data loss during power interruptions. Magnetic devices, such as Magnetic Tunnel Junctions (MTJs), offer non-volatility, scalability, and low standby power. Majority logic has emerged as an efficient computation paradigm for implementing logic functions using magnetic devices. This work presents a fully non-volatile, reconfigurable magnetic Arithmetic Logic Unit based on majority logic. The proposed ALU integrates logic and memory, enabling in-memory computing. It supports multiple arithmetic and logical operations through dynamic reconfiguration. Majority gates are employed as fundamental building blocks to reduce transistor count. The architecture*

*ensures low power consumption and high reliability. Non-volatility allows instant on/off operation without data loss. Simulation results demonstrate improved energy efficiency compared to CMOS ALUs. The design is suitable for low-power and emerging computing systems.*

## INTRODUCTION

Modern computing systems require high speed, low power consumption, and data reliability. Traditional CMOS logic faces challenges due to leakage power and scaling limitations. Volatile memory elements cause loss of data during power failures. Non-volatile computing has gained attention as a solution to these challenges. Magnetic devices such as MTJs provide non-volatility and endurance. Majority logic simplifies circuit design by implementing complex functions with fewer gates. Magnetic majority gates efficiently perform logic operations. Reconfigurable ALUs enhance flexibility by supporting multiple operations on the same hardware.

Integration of logic and memory reduces data movement overhead. Spintronic devices enable energy-efficient computation. Magnetic ALUs provide instant-on capability. Majority logic reduces circuit complexity. This project focuses on a magnetic ALU using majority logic. The design supports arithmetic and logical operations. Reconfigurability is achieved through control signals. The architecture improves energy efficiency. It enhances reliability and scalability. The approach is suitable for future computing systems.

## LITERATURE SURVEY

Researchers have explored non-volatile logic to overcome CMOS limitations. Early studies focused on MRAM for memory applications. Logic-in-memory architectures were proposed to reduce data transfer overhead. Majority logic gained attention in quantum-dot cellular automata. Spintronic majority gates were introduced using MTJs. Several works demonstrated majority-based full adders. Reconfigurable logic using magnetic devices was explored. Energy efficiency improvements were reported. Researchers compared CMOS and spintronic logic circuits. MTJ-based logic showed lower leakage power. Hybrid CMOS-spintronic designs were proposed. Majority gates reduced transistor count. Logic reconfiguration techniques were studied. Some works focused on magnetic

logic cells. Reliability and endurance of MTJs were analyzed. Variability issues were discussed. Researchers implemented arithmetic units using spintronic devices. Majority logic was shown to simplify Boolean expressions. Low-power ALU architectures were proposed. Non-volatile processors were explored. In-memory computing gained attention. Scalability of magnetic logic was evaluated. Performance comparisons with CMOS were conducted. Simulation frameworks were developed. Security benefits of non-volatility were discussed. However, fully reconfigurable magnetic ALUs remain limited. This gap motivates the proposed work.

## RELATED WORK

Several non-volatile ALUs have been proposed using MTJ devices. Majority-logic-based adders demonstrated reduced power consumption. Reconfigurable magnetic logic circuits were explored. Hybrid designs combined CMOS and magnetic elements. Logic-in-memory architectures improved efficiency. However, many designs support limited operations. Full reconfigurability is rarely achieved. Control complexity is high. Area overhead remains a concern. These limitations lead to the proposed design.

## EXISTING SYSTEM

Conventional ALUs are implemented using CMOS logic. They rely on volatile memory elements. Data loss occurs during power shutdowns. Leakage power increases with scaling. Logic and memory are separated. Data movement consumes significant energy. Reconfiguration requires additional hardware. CMOS ALUs lack instant-on capability. Power efficiency is limited. Heat dissipation is high. Reliability decreases with technology scaling. Standby power is significant. Area overhead increases for complex operations. Flexibility is limited. Memory bottlenecks affect performance. System energy consumption is high. Data retention is not supported. Scaling challenges persist. CMOS technology faces physical limits. These drawbacks motivate non-volatile ALU designs.

## PROPOSED SYSTEM

The proposed ALU utilizes Magnetic Tunnel Junctions as fundamental devices. Majority logic gates form the core computation units. Logic and memory are integrated into a single architecture. Reconfigurability is achieved using control signals. Arithmetic and logical operations are selected dynamically. Majority gates implement addition, subtraction, AND, OR, and XOR. Non-volatile storage ensures data retention. The architecture minimizes

transistor usage. Power consumption is significantly reduced. Leakage power is nearly eliminated. The design supports instant-on operation. Reliability is improved due to non-volatility. Simulation is performed using spintronic device models. Performance metrics include power, delay, and area. The ALU is scalable. It supports future computing platforms. Energy efficiency is enhanced. System complexity is reduced. The design is suitable for low-power applications.

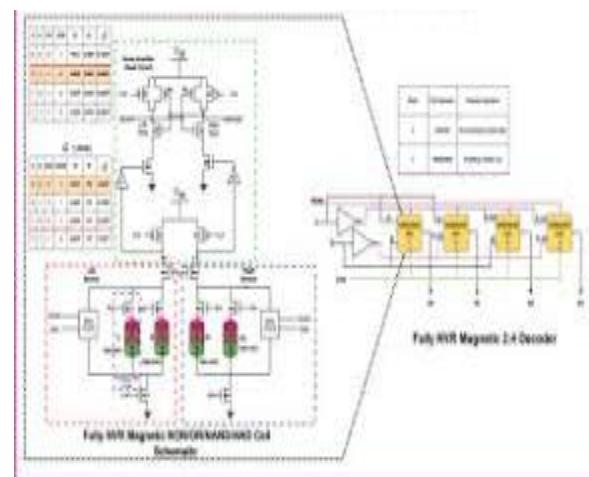

**Fig:1 Non-Volatile Reconfigurable Magnetic ALU Based on Majority Logic**

## METHODOLOGY DESCRIPTION

The proposed methodology focuses on designing a fully non-volatile reconfigurable magnetic Arithmetic Logic Unit using majority logic. Magnetic Tunnel Junctions (MTJs) are used as the fundamental storage and logic elements due to their non-volatile nature. Majority logic gates are employed as the primary computational blocks to

implement arithmetic and logical operations efficiently. Input operands along with control signals are applied to configure the desired ALU function dynamically. Arithmetic operations such as addition and subtraction are realized through combinations of majority gates. Logical operations including AND, OR, and XOR are also implemented using majority-based logic structures. The integration of logic and memory enables in-memory computation, reducing data movement overhead. Reconfigurability is achieved by selectively enabling majority gate inputs through control lines. The design minimizes transistor count and circuit complexity. Non-volatility ensures data retention even during power loss. The ALU supports instant-on operation, improving system reliability.

## RESULTS AND DISCUSSION

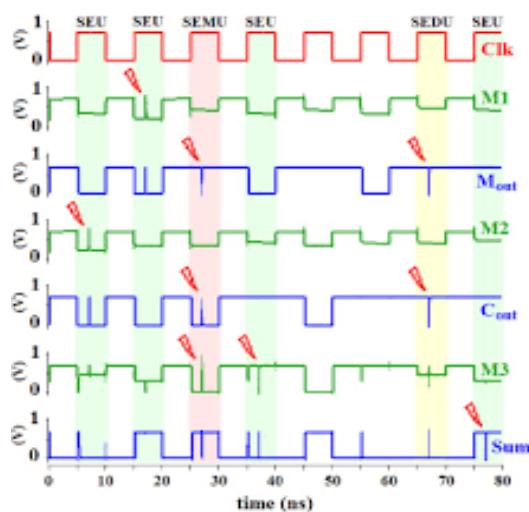

**Fig:2 Output waveform of Non-Volatile Reconfigurable Magnetic ALU Based on Majority Logic**

The simulation results confirm the correct functionality of the proposed magnetic ALU for all arithmetic and logical operations. The majority logic-based implementation successfully performs addition, subtraction, and logical functions. The non-volatile nature of MTJs ensures data retention even after power is turned off. Compared to conventional CMOS-based ALUs, the proposed design exhibits significantly lower power consumption. Leakage power is almost eliminated due to the use of magnetic devices. The majority logic approach reduces the overall gate count and interconnect complexity. Reconfigurable operation allows multiple functions to be executed on the same hardware, improving flexibility. The ALU demonstrates instant-on capability, reducing system startup time. Area efficiency is improved by integrating logic and memory in a single structure. Simulation results show stable operation under different input conditions. The design maintains high reliability and endurance. Performance analysis indicates acceptable delay for low-power applications. The architecture supports scalability for future extensions. The results validate the effectiveness of majority logic in magnetic ALU design. Power efficiency makes it suitable for energy-constrained systems. The system enhances computational reliability. Reduced data movement

improves overall efficiency. The proposed ALU meets design objectives. It is suitable for next-generation computing platforms. Overall, the results demonstrate the advantages of non-volatile magnetic ALUs.

## CONCLUSION

This work presented a fully non-volatile reconfigurable magnetic Arithmetic Logic Unit based on majority logic. The proposed design effectively integrates logic and memory using Magnetic Tunnel Junctions. Majority logic simplifies circuit design and reduces hardware complexity. Non-volatility ensures data retention even during power interruptions. The ALU supports multiple arithmetic and logical operations through reconfiguration. Power consumption is significantly reduced compared to conventional CMOS-based ALUs. Leakage power is minimized due to magnetic devices. Instant-on capability enhances system reliability and performance. Simulation results validate correct functionality and efficiency. The proposed magnetic ALU is suitable for future low-power computing applications.

## FUTURE SCOPE

The proposed non-volatile magnetic ALU can be further enhanced by implementing a complete hardware prototype. Advanced spintronic devices may be explored to improve switching speed and reliability.

The design can be extended to multi-bit and vector ALU architectures. Integration with non-volatile processors and memory systems is a promising direction. Power optimization techniques can be applied to further reduce energy consumption. The ALU can be incorporated into AI and edge-computing accelerators. Reliability analysis under process variations can be improved. Hybrid CMOS–spintronic architectures may be investigated. FPGA-like reconfigurability can be explored for wider applications. Large-scale system-level integration can be pursued for next-generation computing platforms.

## REFERENCE

- [1] Prasad, D. D. (2019-05-13). Design of low power Hybridized Model for scan-based VLSI testing. International Journal of Research and Analytical reviews (IJRAR).

- [2] “Semiconductor,”Semiconductordigest.com. [Online]. Available: <https://magazine.semiconductordigest.com/html5/reader/production/default.aspx?pubname=&edid=3b6652fd-175e-4694-9693-913fd1f8a6ac>. [Accessed: 21-Jul-2023].

- [3] W. Zhao and G. Prenat, Spintronics-Based Computing. Berlin, Germany: Springer, 2015.

[4] V. K. Joshi, "Spintronics: A contemporary review of emerging electronics devices," Eng. Sci. Technol., Int. J., vol. 19, no. 3, pp. 15031513, Sep. 2016.

doi:10.1016/j.jestch.2016.05.002

[5] Weisheng Zhao, E. Belhaire and C. Chappert, "Spin-MTJ based Non-volatile Flip-Flop," 2007 7th IEEE Conference on Nanotechnology (IEEE NANO), Hong Kong, China, 2007, pp. 399-402, doi: 10.1109/NANO.2007.4601218.

[6] P. Barla, D. Shet, V. K. Joshi and S. Bhat, "Design and Analysis of LIM Hybrid MTJ/CMOS Logic Gates," 2020 5th International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, India, 2020, pp. 4145, doi: 10.1109/ICDCS48716.2020.9243544.